|

|

|

|

|

|

2004年度前期 IT教育基礎論特論B

コンピュータによる情報処理の基礎となっている命題論理、 およびこれを代数により表現するブール代数を理解する。

コンピュータシステムは、様々な複雑な情報処理を行うことが可能であるが、 基本的には、極単純な論理回路を組み合わせることによりこれを実現している。 本講義では、コンピュータによる情報処理の仕組みを理解するために、 コンピュータを構成する論理回路の基礎である命題論理、 ならびにこの命題論理を代数の形で表現したブール代数について学習する。

命題論理とは記号論理の1つである。 命題とは、何らかの事象に対する言明であり、 その言明が真(正しい)であるか偽(誤り)であるかを 一意に決めることができるものである。 また論理とは、何らかの事象や条件から何が推論されるかを求めるものであり、 記号論理では、これを記号により表現する。 すなわち命題論理では、なんらかの事象や条件を命題としてとらえ、 その命題が真(正しい)であるか偽(誤り)であるかを 論理式として記号により表現する。

命題論理では、命題に対する論理を論理記号を用いて論理式として表現する。 例えば、ある命題X と別の命題Y があり、 「X が真ならばY が真である」 ことが成り立つか否かを示す論理は、以下のような論理式として表現される。

| X → Y |

命題論理で定義されている論理記号を表1に示す。

| 論理記号 | 意味 | 論理式の例 |

|---|---|---|

| ¬ | 否定(negative) | ¬X |

| ∧ | 論理積(conjunction) | X ∧Y |

| ∨ | 論理和(disjunction) | X ∨Y |

| →(⇒) | 含意(implication) | X →Y |

| ≡(⇔) | 同値(equivalency) | X ≡Y |

命題論理における論理式の真偽は、その要素となる命題の真偽によって決まる。 例えば、真を「T(True)」、偽を「F(False)」と表したとして、 論理式「X ∧ Y 」の真偽は 命題X 、Y の真偽に応じて表2のようになる。 このような、命題の真偽に基づく論理式の真偽をまとめた表を真理値表という。

| X | Y | X ∧ Y |

|---|---|---|

| F | F | F |

| F | T | F |

| T | F | F |

| T | T | T |

表3に、各論理記号に対する論理式の真理値表をまとめたものを示す。

| X | Y | ¬X | X ∧ Y | X ∨ Y | X → Y | X ≡ Y |

|---|---|---|---|---|---|---|

| F | F | F | F | F | T | T |

| F | T | F | T | T | F | |

| T | F | T | F | T | F | F |

| T | T | T | T | T | T |

X →Y という論理式は、X ならばY が 常に成り立つということを意味しているわけではなく、 X とY の真偽により、 X →Y の真偽が定まることに注意が必要である。 例えば、命題X が真であり、同時に命題Y が真であれば、 X → Y は真であるといえる。 もしX が真であり、Y が偽であれば、 X → Y は成り立っていないことになるので、偽となる。 逆に、X が偽であれば、Y の真偽に関わらず、真となる。

ここでもう1つ注意しなければならないのは、 X が偽の場合、Y の真偽に関わらず、 X → Y は真であるという点である。 直感的には、X → Y は、 X が偽であればY も偽であるように思われるかもしれないが、 X → Y の意味するところは、 「X が真ならばY が真であることが成り立っている」 かどうかであり、 X が偽である場合のことは問われていない。 すなわち、Y が真であろうと偽であろうと、 この論理式は成り立っていることになり、真となる。

ブール代数とは、0もしくは1に対し、論理演算を行い、 単項演算子NOT( )、 二項演算子AND(・)、OR(+)による演算を行い、 結果として0もしくは1の値を得る代数系である。 ブール代数は、命題論理における真偽をそれぞれ1および0とし、 また、否定、論理積、論理和の各論理記号を それぞれNOT、AND、ORの演算子に置き換えたものともいえる。

ブール代数における演算子を表3に示す。

| 演算子 | 意味 | 演算式の例 |

|---|---|---|

| NOT (negative) | X | |

| ・ | AND (conjunction) | X ・Y |

| + | OR (disjunction) | X +Y |

| = | EQUAL (equivalency) | X =Y |

命題の真偽やブール代数の1、0を電気信号のON、OFFとして入力し、 命題論理やブール代数に基づく論理演算を行なう電子回路を論理回路と呼ぶ。 論理回路では、論理演算の結果を同様に電気信号のON、OFFとして出力する。 コンピュータシステムを構成するCPUなどの電子部品は、 様々な論理回路により実現されている。

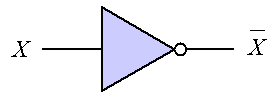

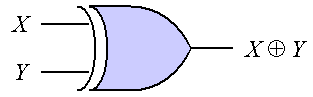

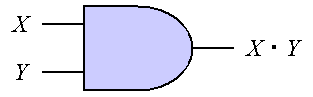

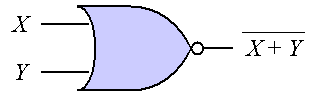

論理回路は、基本的な論理演算を行う 論理ゲート(基本素子)を組み合わせることにより実現される。 命題論理の真偽やブール代数の1、0を電気信号のON、OFFとして入力し、 論理演算を行った結果を電子回路を論理回路と呼ぶ。 論理回路は、基本的な論理演算を行う 論理ゲート(基本素子)を組み合わせることにより実現される。 論理ゲートには、否定(NOT)や論理積(AND)、論理和(OR)に加え、 排他的論理和(XOR)や論理積の否定(NAND)、論理和の否定(NOR)などもある。 各種基本論理ゲートを図1に示す(各ゲートの左が入力で右が出力)。

|

|

||

|

|

||

|

|

ここで初めて出てきた排他的論理和とは、 2つの命題X および命題Y において、 どちらか一方が真の場合のみ真となる論理である。 ブール代数では、二項演算子「⊕ (○の中に+)」により表現され、 その真理値表は表4のようになる。

| X | Y | X ⊕ Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

これらの論理ゲートは、それぞれ独立ではなく、 同じ機能を果たす論理回路を他の論理ゲートにより構成することができる。 例えばNANDゲートは、ブール代数で表現すると X ・Y であることから判るように、 図2に示すようにNOTゲートとANDゲートを組み合わせることにより、 同じ機能を果たす論理回路を構成することができる。

|

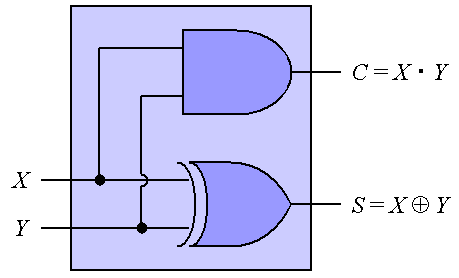

CPUをはじめとする情報処理のための各種電子回路は、 基本的に、論理ゲートを組み合わせた論理回路からなる。 例えば、簡単な例として、 1bitの数値X とY の2つを加算し、 2bitの数値を得る演算を行う論理回路は、 演算結果の上位bitをC 、下位bitをS とすると、 図3のように構成することができ、一般に、これを半加算器(Half Adder)と呼ぶ。

|

この半加算器のC 、S に対する真理値表は、 表5のようになり、確かに1bit同士の数値の加算になることが確認できる。

| X | Y | S =X ⊕Y | C =X ・Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

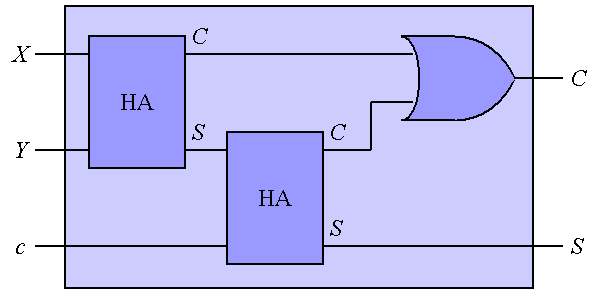

この半加算器を図4に示すように組み合わせると、 下の桁からの繰り上がりを示すc を考慮した 全加算器を構成することができる。

|

この全加算器を複数段組み合わせることにより、 n bitの加算を行う回路を構成できることが容易に想像できる。

ブール代数では、以下の分配則が成り立つ(命題論理も同じ)。

| X ・ (Y + Z ) = (X ・Y ) + (X ・Z ) |

| X + (Y ・ Z ) = (X +Y ) ・ (X +Z ) |

また排他的論理和(⊕)は、 ブール代数により以下のように定義することができる。

| X ⊕Y = (X +Y ) ・ (X ・Y ) |

これに基づき、以下の問いに答えよ。

X およびY に対する、 X +Y 、 (X ・Y )、および (X +Y ) ・ (X ・Y ) の真理値表を作成し、 表4で示したX ⊕Y の真理値表と一致することを確認せよ。

分配側を利用すると、排他的論理和(⊕)を 以下のように表記できることを示せ。

| X ⊕Y = (X ・Y ) + (X ・Y ) |

一般に、コンピュータのCPUなどを構成するICやLSIでは、 製造が容易なNANDゲートを組み合わせて構成されている。 すなわち、NOT、AND、OR、NOR、XORなどの全ての論理回路を NANDゲートのみの組み合わせにより実現することができる。 例えば、NOTゲートと同じ機能を果たす論理回路が NANDゲートを利用して構成できることは、 NOT演算がブール代数を用いて X = (X・X) のように表記できることからもわかり、 これに基づき図5のように論理回路を構成できる。

|

これを参考にし、以下の問いに答えよ。

ANDゲートと同じ機能を果たす論理回路をNANDゲートにより構成できることを ブール代数により示せ。 また、ANDゲートと同じ機能の論理回路をNANDゲートにより構成し、図示せよ。

ORゲートと同じ機能をNANDゲートにより構成できることをブール代数により示せ。 また、ORゲートと同じ機能の論理回路をNANDゲートにより構成し、図示せよ。

全加算器は、加算する2つの数値のn 桁目の値X およびY 、 ならびに下の桁からの繰り上がりを示すcの3つの入力に対し、 和を示すS 、および次の桁への繰り上がりを示すC を出力する。 X 、Y 、c の組み合わせに対する S およびC の真理値表を示せ。

半加算器と全加算器を組み合わせ、 2bitで表現される数値x およびy を足し合わせ、 (最大)3bitの値z を出力する演算を行なう論理回路を構成し、図示せよ。 このとき、入力値x の1桁目をXL 、2桁目をXH 、 y の1桁目をYL 、2桁目をYH 、 演算結果z の1桁目をZL 、2桁目をZM 、 3桁目をZH とし、図中に明記せよ。 また、XL 、XH 、YL 、YH の入力に対する ZL 、ZM 、ZH の真理値表を示せ。

なお半加算器および全加算器の内部の論理回路を図中に示す必要はないが、 それぞれの論理回路の出力C およびS を 図4の全加算器の論理回路図における半加算器の使用方法と同様に明記せよ。

良さそうな参考文献をまだ探していません...。